# 九州大学学術情報リポジトリ Kyushu University Institutional Repository

# ディジタル無線通信用FFT回路のビット幅制御による 低消費エネルギー化手法の検討

徳永, 将之 九州大学大学院システム情報科学府

樽見,幸祐 九州大学大学院システム情報科学府

安浦, 寛人 九州大学大学院システム情報科学研究院

https://hdl.handle.net/2324/6242

出版情報:電子情報通信学会技術研究報告, SDM2005-129, ICD2005-68. 105 (234), pp.7-12, 2005-08. 電子情報通信学会ICD研究会

で、に転送に バージョン: 権利関係:

# ディジタル無線通信用 FFT 回路の ビット幅制御による低消費エネルギー化手法の検討

徳永 将之 博見 幸祐 安浦 寛人 草

† 九州大学大学院システム情報科学府

〒816-8580 福岡県春日市春日公園 6-1 1 九州大学大学院システム情報科学研究院

〒816-8580 福岡県春日市春日公園 6-1

E-mail: † { tokunaga,tarumi}@c.csce.kyushu-u.ac.jp, ‡ yasuura@c.csce.kyushu-u.ac.jp

**あらまし** 近年,ディジタル無線通信の普及が進んでいる.ディジタル無線通信はその性質上携帯機器での利用も多く,バッテリ容量等の制約のため低消費エネルギーであることが求められる.本稿では,OFDM(Orthogonal Frequency Division Multiplexing)伝送方式で利用される FFT(Fast Fourier Transform)演算回路において,消費エネルギーと通信の品質の関係性について考察し,消費エネルギーの削減の方針の検討を行う.通常,FFT 演算器では内部の計算を全て同じ演算精度で行っている.しかし,結果にあまり影響しない演算箇所があるならばその演算のビット幅を削減することで消費エネルギーの削減が可能であると考えられる.FFT 演算器のバタフライ演算において演算のビット幅を変えたときの消費エネルギーを測定した.64-ポイント FFT 演算を用いた OFDM 送受信処理においてビット幅をステージごとに変化させ BER(Bit Error Rate)の変化を観察した.これにより,ビット幅を変化させることによる低消費エネルギー化が可能であり,FFT 演算内部でのビット幅の与え方により BER が異なることを確認した.

キーワード 低消費エネルギー化、OFDM.FFT.ビット幅

# An examination on the method of Energy reduction with bit width control in FFT circuits for digital wireless communications

Masayuki TOKUNAGA<sup>†</sup> Kosuke TARUMI<sup>†</sup> and Hiroto YASUURA<sup>‡</sup>

† Graduate school of Information Science and Electrical Engineering, Kyushu University

6-1, Kasuga-Koen, Kasuga, Fukuoka, 816-8580, Japan

‡ Graduate school of Information Science and Electrical Engineering, Kyushu University 6-1,Kasuga-Koen, Kasuga, Fukuoka, 816-8580, Japan

E-mail: † {tokunaga, tarumi}@c.csce.kyushu-u.ac.jp ‡yasuura@c.csce.kyushu-u.ac.jp

**Abstract** Recently, digital wireless communication systems become very popular to use in portable devices. Low-energy system implementation is strongly required because of the battery restriction or the power source restriction. In this paper, we discuss the effectiveness of controlling the bitwidth of FFT (Fast Fourier Transformation) circuits in OFDM(Orthogonal Frequency Division Multiplexing) based digital wireless communication systems. We show the experimental results of trade-offs between BER(Bit Error Rate) and energy consumption by changing the bitwidths of butterfly modules in FFT.

Keyword Low Energy Consumption, OFDM, FFT, bitwidth

### 1. はじめに

近年、ディジタル無線通信の普及は進んでおり、その応用範囲も携帯電話、無線 LAN,RFID など多岐にわたる.こうした無線通信機器は携帯する形で利用されることが多い.携帯機器では大半の場合バッテリのサイズや容量の制限が存在することから低消費エネルギー

であることが求められている.その為,ディジタル無線通信用 LSI に対する低消費エネルギー化への要求は強い

ディジタル無線通信の伝送方式の中でも現在注目 されている方式に OFDM(Orthogonal Frequency Division Multiplexing)がある.これは高速なデータ列を 複数の低速なデータ列に分割して並列に送受信することによりデータを高速に送受信する方式である.現在 OFDM は無線 LAN 規格 IEEE802.11a/g,地上ディジタル 放送等に利用されており,今後ますますその重要性は 増すものと考えられる.そこで,本稿では OFDM 送受信用 LSI の低消費エネルギー化を目指す.

OFDM での処理のうち、ディジタル部において大きな消費エネルギーを占めるものの一つに FFT(Fast Fourier Transform)、IFFT(Inverse Fast Fourier Transform) 演算がある.FFT、IFFT 演算は OFDM 送受信において必須の処理であり、これらの演算器における消費エネルギーは OFDM システムを使用する移動体端末に要求される消費電力のうち約 20%を占めるともいわれている[1].そのため OFDM 全体の低消費エネルギー化のために FFT 演算器の低消費エネルギー化は必要である.

FFTを設計する際に考慮しなければならないものの中に演算精度がある。一般的に演算に用いるビット幅によって演算精度は決定されるが、演算精度を上げるためにビット幅を増加させると回路規模が増大し、回路の消費エネルギーが増加する。また、ビット幅を削減し演算精度を下げると通信における誤りが生じ、BER (Bit Error Rate)が大きくなり、通信が正しく行えない可能性が生じる。そのため、回路規模や消費エネルギーと演算精度のトレードオフを考慮して設計しなければならない[2]。また、ソフトウェアにおいて演算に用いるビット幅を変化させ、低消費エネルギー化を行う手法も提案されている[3]。

しかしこうした通常の FFT 演算器では,FFT の内部の演算は全て一律のビット幅を与えている.しかし,FFT 演算において高い演算精度を必要とする演算やそれほど精度が必要でない演算が混在している場合,必要以上に高い精度で演算を行う部分が存在する.その部分の演算でのビット幅を変化させることで回路規模が縮小し,トランジスタのスイッチング回数が減少すると考えられる.

そこで本稿では、FFT 演算の内部においてビット幅を変化させたときに消費エネルギーと通信におけるBER が変化することを確認する.これにより、消費エネルギーと BER の間にトレードオフが存在することを確かめる.また、FFT 演算の内部の演算を全て同じビット幅で行うのではなく、ステージごとにビット幅を指定することでFFT演算の内部で高い精度を必要とする箇所を探す

本稿の構成を以下に示す.まず 2 章で消費エネルギーモデルと OFDM の通信での処理の説明を行う.3 章でビット幅を変化させることによる消費エネルギーとBER の変化ついての説明を行い,4 章で実験を行いそれらの要素が FFT 内部でビット幅を変化させたときどの

ように変化するかを確認する.最後に 5 章で本稿をまとめ今後の課題を述べる.

### 2. 準備

# 2.1.消費エネルギーモデル

[4]では、CMOS 集積回路の消費電力 p について定義されている。その定義より、  $E=\int pdt$  の計算を行うことで全体の消費エネルギー E を求めると、次式のようになる.

$$E = E_{sw} + E_{sc} + E_{leak}$$

ここで

$E_{sw}$ :トランジスタのスイッチング時における負荷容量への充放電による消費エネルギー

$E_{sc}$ : 貫通電流による消費エネルギー

$E_{leak}$ : リーク電流による消費エネルギー

である.またこのうち,あるタスクを行うときの $E_{\mathrm{sw}}$ は

$$E_{sw} = \sum_{i} Sw_{i} C_{LDi} V_{dd}^{2}$$

$Sw_i$ : i 番目のトランジスタの総スイッチング回数

$C_{IDi}$ : i 番目のトランジスタの負荷容量

$V_{dd}$ :電源電圧

と表される.本稿では,総スイッチング回数を削減することにより  $E_{sw}$ を削減し低消費エネルギー化を行うことを目標とする..

# 2.2. OFDM 処理

#### 2.2.1 変調,復調

ディジタル通信において,送信すべきディジタルデータをアナログ信号である搬送波で表現することを変調という.逆に変調された信号から元のデータを取り出すことを復調という.OFDM を用いて通信を行う規格の一つ,IEEE802.11aでは

- · BPSK(Binary Phase Shift Keying)

- · QPSK(Quadrature Phase Shift Keying)

- 16QAM(16 Quadrature Amplitude Modulation)

- 64QAM(64 Quadrature Amplitude Modulation)

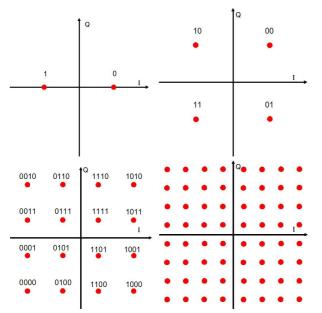

の4種類の変調方式が規定されている.これらの変調の IQ(In-phase, Quadrature)平面での様子を図1に示す. このような IQ 平面にプロットされた搬送波の1単位をシンボルと呼ぶ.

図 1: BPSK(左上),QPSK(右上),16QAM(左下),64QAM(右下)

図1のように BPSK,QPSK はデータによって搬送波の位相を変化させ,16QAM,64QAM は搬送波の同相成分,直交成分の振幅を変化させる.変調方式ごとにシンボル間の距離が異なり,外部雑音等の影響によりシンボル間の半分以上の誤差が発生した場合,復調時に誤りが生じる.そのため,シンボル間距離の大きい変調方式ほど復調時の誤りが少ない.1シンボルごとに BPSK は1ビット,QPSK は2ビット,16QAM は4ビット,16QAM は6ビットの情報量をもち,シンボルあたりの情報量が多いほどシンボル間距離は小さくなり誤りは増加する.ビットあたりの復調の誤り率をBERで表す.ディジタル通信では送信データと受信データが一致するのが基本であるため,これらの誤りはエラー訂正符号等を用いて訂正する必要がある.

## 2.2 FFT,IFFT

$x_{[n]}$ を入力, $X_{[m]}$ を出力としたときの N-ポイント

DFT (Discrete Fourier Transform)の計算式は以下のように表される.

$$X_{[m]} = \frac{1}{N} \sum_{n=0}^{N-1} x_{[n]} W_N^{mn}$$

ここで W は回転因子と呼ばれ,

$$W_N = \exp(-\frac{j2\pi}{N})$$

である.FFT は DFT の計算の順序を工夫することにより計算量を削減するアルゴリズムである.FFT の演算は 2 入力バタフライ演算の組み合わせで行われてい

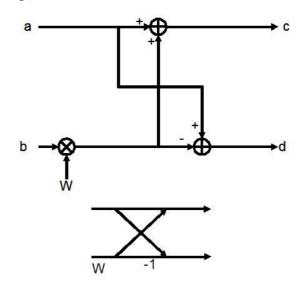

る.2入力バタフライ演算は図2に示すような演算である。

図2:2入力バタフライ演算

なお,a,b は入力,W は回転因子,c,d は出力である.また,この演算での入力から出力までを 1 ステージとする.N-ポイントFFTの場合,N/2個の2入力バタフライ演算器を並列に並べ,それらを直列に $\log_2 N$ ステージ

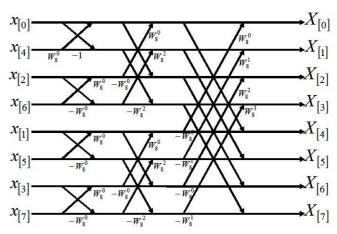

繋げる.よってバタフライ演算は合計  $(N\log_2 N)/2$  回行われる.8-ポイント FFT の場合,図 3 のようになる.図 3 では,4 個の 2 入力バタフライ演算器 3 ステージで構成されている.

図 3:8-ポイント FFT におけるバタフライ演算

# 3. ビット幅制御による低消費エネルギー化

FFT 演算では有限長ビットを用いて演算を行っているため,演算誤差が発生する[5].この大きさは用いるビット幅に依存している.また,回路の消費エネルギーもまたビット幅によって変化する.この性質を利用した

低消費エネルギー化についての考察を行う.

#### 3.1. 概要

FFT 演算器での演算に用いるビット幅は通常,回路規模や消費エネルギーとのトレードオフを考慮して決定されている。演算でのビット幅を削減すると回路規模が縮小し,トランジスタのスイッチング回数が減少するため消費エネルギーが減少する.しかし,ビット幅を変化させることにより演算誤差が増大し BER が増加する.

通常 FFT 内部の演算は全て同じビット幅を用いて行われている.もし,FFT のある一部の演算において,その箇所での演算誤差が通信での BER に与える影響が小さい場合,その演算のビット幅を削減することで低消費エネルギー化が可能となる.

そのためには FFT 演算のどの箇所が通信において重要かを考えなければならない.また,OFDM では変調方式が複数あり,変調方式によってシンボル間距離が異なるためそれぞれの場合において演算誤差の BER への影響は異なると考えられる.また,通信環境に存在する外部雑音の強度によっても異なると考えられる.

よって、これらの要素を考慮し演算誤差のBERへの影響を考える.

#### 3.2. 理論的考察

FFT 演算器の消費エネルギー,演算誤差について以下のように考える.

まず以下のように仮定する.

- ・ ビット幅は 2 入力バタフライ演算器 N/2 個の 1 ステージごとに変化させるとする.

- バタフライ演算器の入力,回転因子の下位ビット を論理値"0"にマスクすることでビット幅を削減 する。

また,次のように定義する.

- ・ $E_b$ : 2 入力バタフライ演算一つあたりの消費エネルギー

- ・ $E_{bi}$ : i 番目の 2 入力バタフライ演算器の消費エネルギー

- ・  $\Delta E$  : ある基準からの FFT 演算器の消費エネルギーの削減量

- ・ $X = \{x_{[1]}, x_{[2]}, \dots x_{[N]}\}^T$ : FFT 入力ベクトル

- ・ $Y = \{y_{111}, y_{121}, ..., y_{1N1}\}^T$ : FFT 出力ベクトル

- ・W:回転因子を含む行列.Y=WXを満たす

- ・ n<sub>(t)</sub>: 時刻 t に混入する外部雑音

・

$$S_i$$

:  $W$ の i 番目のステージの要素. $W = \prod_{i=1}^{\log_2 N} S_i$

$$T_i := S_i \cdot T_{i-1} (T_0 = X, T_{\log_2 N} = Y)$$

・  $\Delta Y, \Delta W, \Delta S_i, \Delta T_i$ : それぞれ  $Y, W, S_i, T_i$  を有限長ビットを用いて表した時の誤差

このとき,基準となる N-ポイント FFT 演算器を考える.この演算器では FFT 全体を通してある一つのビット 幅 で 演 算 を 行 っ て い る と す る . FFT で は  $\left(N\log_2 N\right)/2$ 回 2 入力のバタフライ演算を行う必要があり,FFT のバタフライ演算部の消費エネルギーは

$$\frac{N\log_2 N}{2}E_b$$

2 入力バタフライ演算器ごとにビット幅を変化させるとき,基準と比較しての消費エネルギーの削減量  $\Delta E$

$$\Delta E = \frac{N}{2} \left( E_b \log_2 N - \sum_{i=1}^{\log_2 N} E_{bi} \right)$$

となる.

また,ビット幅を変化させたときの BER の増加量を 考える.まず,FFT 演算を

$$Y = WX + n_{(t)}$$

と表す.今,通信の受信処理におけるFFTのビット幅を 理想的な状態から変化させると

$$W + \Delta W = \prod_{i=1}^{\log_2 N} (S_i + \Delta S_i)$$

のように誤差が発生する.このときの $\Delta T_i, \Delta Y$ を考える.

$$T_1 + \Delta T_1 = (S_1 + \cdot \Delta S_1) \cdot X \updownarrow \emptyset$$

$$\Delta T_1 = \Delta S_1 X$$

となる.同様に

$$T_i + \Delta T_i = (S_i + \cdot \Delta S_i) \cdot (T_{i-1} + \Delta T_{i-1})$$

$$\Delta T_i = S_i \Delta T_{i-1} + \Delta S_i T_{i-1} + \Delta S_i \Delta T_{i-1}$$

となり、 $\Delta Y$ は

$$\begin{split} Y + \Delta Y &= T_{\log_2 N} + \Delta T_{\log_2 N} \\ \Delta Y &= S_{\log_2 N} \Delta T_{\log_2 N - 1} + \Delta S_{\log_2 N} T_{\log_2 N - 1} \\ &+ \Delta S_{\log_2 N} \Delta T_{\log_2 N - 1} \end{split}$$

となる.ビット幅を変化させることによりこの誤差が変化し,BERが増減する.

### 4. 実験

- 3 章での仮定条件下においてビット幅を変化させる ことによる影響を実験にて確認する.すなわち

- 1.ビット幅と消費エネルギー

- 2.ビット幅と BER

の関係が存在し、なおかつ消費エネルギーとBERにトレードオフの関係が存在することを確認する.なお、ここで考えるFFT演算器は64-ポイントのものであり、2入力のバタフライ演算器が32個並列に並び、それを直列に6ステージ繋げたものとする.

#### 4.1. 消費エネルギーの変化

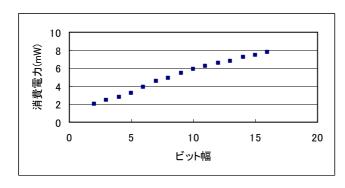

ビット幅の変化による消費エネルギーの変化を実験によって確認する.2 入力バタフライ演算にランダムな入力を与え,下位ビットを 0 にマスクすることにより演算のビット幅を変化させ,消費電力を測定する.回転因子は 64-ポイント FFT において使用される回転因子を用いた.回路を 20MHz で動作させたとき,消費電力は図 4 のようになった.使用したツールはケイデンス社の Verilog-XL,及びシノプシス社の Design Compiler, Power Compiler である.また,HITACHI0.18um プロセスの京都大学提供ライブラリを用いた.

図4:バタフライ演算器のビット幅と消費電力

図 4 より,消費電力は入力ビット幅に対してほぼ線形に変化していることがわかる.また,この場合ビット幅を変化させても処理時間は変化しないので消費エネルギーもまたビット幅に対して線形に変化するとする.

よってバタフライ演算器の消費エネルギー $E_b$ を一次関数で近似することができると考えられる.

# 4.2. BER の変化

ビット幅の変化に対する BER の変化を確認するた

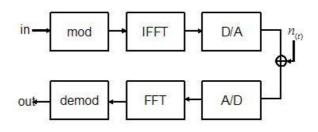

め,以下のような環境でのシミュレーションを行う.まず,図5のようなシステムを考える.

図 5: 実験モデル

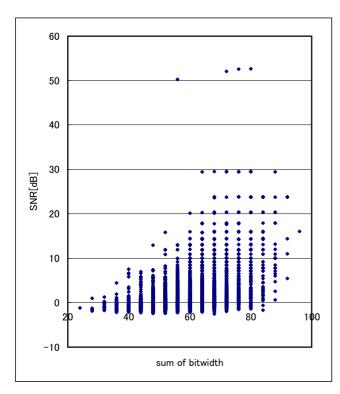

このシステムにおいて、mod は変調 demod は復調、A/D は A/D 変換,D/A は D/A 変換をそれぞれ表している.システムにランダムな入力を与え,変調後の信号と FFT の出力とを比較する.このとき,FFT 演算でのビット幅をステージごとに 4,8,12,16 ビットのいずれかを選択し演算する.理想的には FFT の出力は変調信号と一致するが演算誤差が発生しているため一致しない.このずれを雑音とみなしてそれぞれのビット幅での SNR ( Signal to Noise Ratio ) を求める.SNR は

$$SNR = 20 \log \sqrt{\frac{S}{N}}$$

[dB]

でもとめられる.ここで S,N はそれぞれ信号電力,演算 誤差による雑音の電力である.なお,外部雑音  $n_{(r)}=0$  で

あるとし、変調方式は前述の4種類を考える.このときの BPSK におけるバタフライ演算器での各ステージでの演算に用いたビット幅の和と SNR の関係を図 6 に示す.和を用いるのは前節の実験より2入力バタフライ演算器の消費エネルギーがビット幅に対して線形に変化するとした場合,FFT 演算での消費電力はバタフライ演算器に与えたビット幅の合計に対して線形に変化するためである.このように,与えたビット幅の合計が同じであっても SNR には差が大きく出る.また,SNR が大きい点もあるため,BER を上げずにビット幅を削減することは可能であると考えられる.

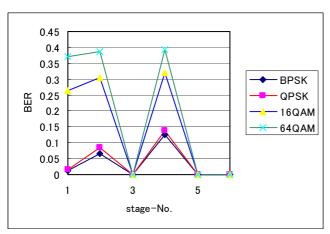

次に、FFT 演算の内部でどのステージの演算においてビット幅の変化が BER の増加に影響するかを調査する.あるステージにおけるビット幅を 4,その他のステージでは 16 として FFT 演算を行い、BER を測定した. 結果は図 7 のようになった. 図 7 における横軸の数値は4ビットのビット幅を与えた FFT のステージ番号を表す.図 7 から 1,2,4 ステージ目での演算のビット幅を削減した場合に BER が大きく変化していることがわかる.このようにステージによってビット幅の BER に対する影響が異なることがわかる.

図 6:ステージごとに与えたビット幅の合計と SNR

図 7:4 ビットで演算を行うステージと BER

# 4.3. 考察

4.2.節の結果から、ビット幅を変化させることにより消費エネルギーと BER が変化することを確認することができた.また、ビット幅を変化させるステージによって BER の変化量が異なることを観察した.これらの性質を利用して低消費エネルギー化を目指す.

BER と消費エネルギーのトレードオフを考慮した上で低消費エネルギー化を行う必要があるが,BER に影響を与えにくい箇所でビット幅を変化させることで効率の良い低消費エネルギー化が可能であると考えられる.また,今回の実験環境では 1,2,4 ステージにおける演算精度が通信において重要で 3,5,6 ステージにお

ける演算は精度を落としても BER にはさほど影響しなかったが,その理由の一つとして演算に与える回転因子の符号化方式が考えられる.今回の実験では回転因子の下位ビットを 0 にマスクしたが,その方式で発生する誤差が 1,2,4 ステージで使用する回転因子では大きくなったと考えられる.このことから,各ビット幅に対する適切な回転因子をあらかじめ準備しておく等,回転因子の符号化を見直すことによってさらに BERを増加させずにビット幅を削減可能であるとも考えられる.

# 5. おわりに

本稿ではOFDMでの通信用FFT演算器において演算のビット幅を適切に変化させることによる低消費エネルギー化について述べ,ビット幅を変化させたときに消費エネルギー,BERが変動することを確認した.また,FFT演算内部においてビット幅の変化に対してBERに影響を与えやすい箇所と与えにくい箇所があることを確認した.今後の課題として,今回確認したBERと消費エネルギーの性質を考慮し,効率の良い低消費エネルギー化を行う回路設計手法の研究を行う.

# 6. 謝辞

本研究は、一部科学研究費補助金(学術創成研究費(2))(課題番号:14GS0218)、および、産学連携研究費福岡県知的クラスタ創成事業「システムLSI設計開発拠点創成」((財)福岡県産業・科学技術振興財団)による.

本研究は東京大学大規模集積システム設計教育研究センターを通し,株式会社日立製作所,シノプシス株式会社,および,日本ケイデンス株式会社の協力で行われたものである.

#### 文 献

- [1] 坪内 和夫,"ブロードバンド&低消費電力ワイヤレス通信 LSI",第 8 回システム LSI ワークショップ,November, 2004

- [2] Kyungtae. Han and B. L. Evans, "Wordlength Optimization with Complexity-And-Distortion Measure and Its Applications to Broadband Wireless Demodulator Design" Proc. IEEE Int. Conf. on Acoustics, Speech, and Signal Proc., May 17-21, 2004, vol. 5, pp. 37-40

- [3] Kyungtae Han, Brian L.Evans, Earl E.Awartzlander, Jr.

"DATA WORDLENGTH REDUCTION FOR

LOW-POWER SIGNAL PROCESSING

SOFTWARE", Proc.IEEE Int. Workshop on Signal

Processing Systems, pp 343-383, Oct. 13-15, 2004.

- [4] Dimitrios Soudris, Christian Piguet and Costas Goutis(Eds.), 'Designing CMOS Circuits for Low power", KLUWER ACADEMIC PUBLISHERS, 2002

- [5] Alan V. Oppenheim, Ronald W. Schafer with John R. Buck "DISCRETE-TIME SIGNAL PROCESSING", Prentice-Hall, 1998.