修士論文要旨(2015年度)

## 忘れられる権利に向けた TLC NAND 型フラッシュメモリの寿命を制御する手法の研究

# Research on Data Lifetime Management Scheme of TLC NAND Flash Memory for Right to be Forgotten

電気電子情報通信工学専攻 竹内研究室 14N5100052K 山沢裕紀

Hiroki YAMAZAWA

#### 1. 研究の背景

Internet of Things(IoT)におけるプライバシー保護は 重要な問題である[1]。インターネット上のプライバシ ーを保護するために忘れられる権利が制定された[2]。 忘れられる権利とは、個人情報などを収集した企業等 に対して個人の意思でその消去を求めることができ る権利である。検索エンジンから個人情報につながる リンクを削除することが可能である。そして、クラウ ドストレージサービスでは、プライバシー保護のため に所定の時間が経過した時に、アップロードした写真 や文書が自動で削除することができる機能が追加さ れた[3]。しかし、実現するためには各々のデータを管 理するためのテーブルが必要となり、管理するファイ ルが多ければテーブルサイズがより増加してしまう。 そこで本研究では、TLC NAND型フラッシュメモ リの寿命の制御を行うために Partial bit-flip(PBF)と  $N_{\text{PBF}}$  page-allocation scheme の 2 つの提案を行った。 これらの提案手法を用いることで、ユーザーが求める 時間に達すると自動で、且つ、物理的にデータが破損 するようになる。そして、管理するファイルの数によ らずテーブルサイズは小さいまま運用が可能となる。

#### 2. NAND 型フラッシュメモリ

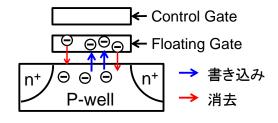

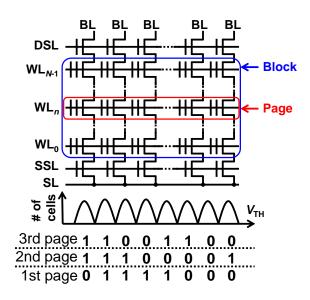

図1にNAND型フラッシュメモリの構造と動作を示す[4]。FN (Fower-Nordheim)トンネリング電流によって電子を浮遊ゲートに注入・放出することでメモリセルのしきい値電圧を変化させ、データを記憶する。FNトンネリング電流は、高電界を浮遊ゲートとシリコン基板の間に加えることによって電子が絶縁膜を通り移動する現象である。そしてTLC NAND型フラッシュメモリは1つのセルに1st、2nd、3rdページと呼ばれる3つのデータを書き込むことができ、ページ単位で書き込みと読み出しを行う。TLC NAND型フラッシュメモリのブロックとページの構造は図2に示す。1ブロック内にあるワードラインは86本あり、各ワードラインに3ページ分データを書くことができるため、

図 1. NAND 型フラッシュメモリの構造と動作

図 2 TLC NAND 型フラッシュメモリのブロック とページの構造[5]

ページ数は258ページである。

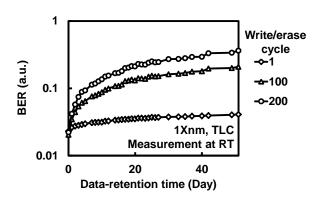

次に、TLC NAND 型フラッシュメモリの信頼性について説明する。図3にTLC NAND 型フラッシュメモリの書き換え回数ごとのデータ保持特性を示す。NAND 型フラッシュメモリは書き込みディスターブエラーとデータ保持エラーにより信頼性が悪化する。データ保持エラーは、書き換え回数増加によるストレスに起因して生じた絶縁膜内のトラップを介して浮遊ゲートから電子が抜け落ち、しきい値電圧が減少するエラーである[6]。そして、時間が経過するにつれ抜け落ちる電子が増加するため、Bit-error rate(BER)が増加する。生じたエラーは誤り訂正符号(ECC)によって訂正される。現在SSDのECCはBose-Chaudhuri-Hocquenghem (BCH)符号が用いられている。BCH符号は、符号語内に生じているエラーは訂

正可能なビット数 (t) までなら元のデータに復元することができる。一方、ビットエラー数が t ビットを超えた場合は元のデータに復元できなくなる。

図3TLC NAND型フラッシュメモリの 各書き換え回数におけるデータ保持特性

### 3.TLC NAND 型フラッシュメモリの寿命を制御する 手法

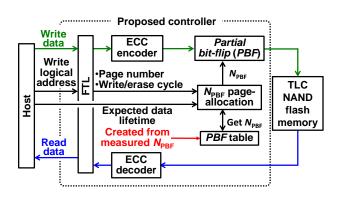

図4に提案するコントローラを示す。BCH 符号による訂正可能なエラー数と、NAND 型フラッシュメモリのデータ保持特性からデータの最大寿命が決定される。提案する手法はこの特性を利用し、書き込み時のデータに意図的にエラーを注入することでデータの寿命の制御を行う。書き込みを行う際、まずホストから書き込みを行う際、まずホストから書き込みでうり際、まずホストから書き込みででうりでできて、からでができでです。「7」、得られた情報より、PBF テーブルからページ番号と書き換え回数、そして、ホストから得られたターゲット寿命をもとに注入するエラーの量(MPBF)が選択される。必要な MPBF が決定したら、ECC エンコードされたデータに対して、各ページのデータに MPBF だけビットを反転し TLC NAND 型フラッシュメモリへと書き込

図4 提案するコントローラ

みを行う。ターゲット寿命の時間が経過した後にデータが読み出されると、誤り訂正限界を超えたビットエラーが生じているため、元のデータに戻すことができずにエラーが生じた状態のままデータがホストへと送られる。したがって、提案するコントローラは、一タは自動的に破損し、且つ、各ファイルを管理するような大きなテーブルを必要しない。

#### a). Partial bit-flip (PBF)

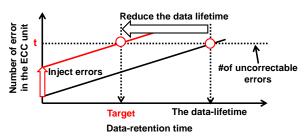

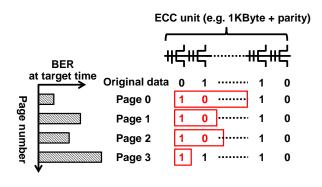

TLC NAND 型フラッシュメモリの寿命を制御する 手法である Partial bit-flip (PBF)の概念図を図5に示す。 エラー! 参照元が見つかりません。図3に示したよう に NAND 型フラッシュメモリに書き込まれたデータ のビットエラーは時間の経過に伴って増加する。PBF は、ターゲット寿命に訂正不可能なエラー数に達する ように符号語内のビットを意図的に反転させる手法 である。この PBFによって、図5のように本来のビットエラーの増加傾向(黒線)が PBFを適用することに より赤線の増加傾向へとシフトし、データ寿命が短く なる。本研究では、ECC のユーザーデータサイズを 1KB とした際の各ページの寿命を評価している。

| Target W/E data-lifetime cycle |     | Write data                      |  |

|--------------------------------|-----|---------------------------------|--|

| Original data                  |     | 01101 1010                      |  |

| 1 month                        | 1   | 10010 1010                      |  |

|                                | 100 | 10010 1010                      |  |

| 1 year                         | 1   | 10011 1010                      |  |

|                                | 100 | 10101 1010                      |  |

| Partial bit-flip<br>(PBF)      |     | ECC unit (e.g. 1KByte + parity) |  |

図 5 Partial bit-flip (PBF)の概念図

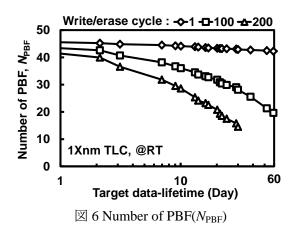

そして、PBF によって反転させるビット量( $N_{\rm PBF}$ )は、書き換え回数やターゲットとするデータ寿命に応じて決められる。図 6 にターゲット寿命ごとの  $N_{\rm PBF}$ を示す。書き換え回数は 1 回、100 回、200 回である。  $N_{\rm PBF}$  はターゲット寿命の増加に伴い減少している。ターゲット寿命が延びれば、ターゲット寿命時の BER

が高くなるため書き込み時に注入する  $N_{PBF}$  は少なくなる。同様に、書き換え回数が増加すると BER も高くなるため  $N_{PBF}$  が小さくなる。したがって、ターゲット寿命が長くなるほど、書き換え回数が大きくなるほど  $N_{PBF}$  の値は小さくなる。これらの測定された  $N_{PBF}$  は、PBF テーブルの作成に用いられる。PBF テーブルとは、書き換え回数とターゲット寿命より  $N_{PBF}$  を選定するテーブルである。

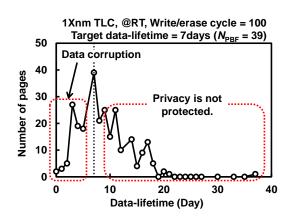

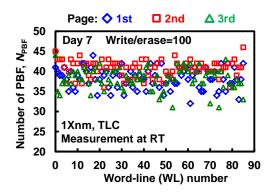

図7にPBFを適用した結果を示す。ターゲット寿命は7日に設定し、書き換え回数は100回である。この時のNPBFは39ビットとなる。図6に示すように、ターゲット寿命と書き換え回数によって決められたNPBFを注入したとしても、ターゲット寿命である7日に達せずに寿命が来たページや、30日以上経過してから寿命が来たページが存在した。データ寿命がターゲット寿命よりも長ければ、プライバシーを保護することはできないため、データ寿命のばらつきを削減する必要がある。

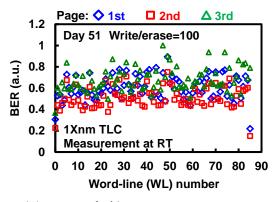

図8にページ番号ごとのBERを示す。TLC NAND型

図 7 ターゲット寿命が 7 日 (N<sub>PBF</sub>=39) における データ寿命のばらつき

フラッシュメモリは 1st、2nd、3rd ページで BER が異なる。特に 2nd ページが 1st、3rd ページよりも BER が低く、端のワードラインの BER が中心のワードラインよりも低くなっている。しきい値電圧の位置によってデータ保持特性が異なることや[8]、1st、2nd、3rd ページのそれぞれの読み出し回数が異なるため BER に差が生じる。したがって、ページの種類に応じて  $N_{PBF}$  を調整する必要がある。

図 8 ページごとの Bit error-rate (BER)

#### b) $N_{\rm PBF}$ page-allocation scheme

図 9 に  $N_{PBF}$  page-allocation scheme を示す。 $N_{PBF}$  page-allocation scheme はデータ寿命のばらつきを削減するための手法である。ページによって異なる BER が生じることから、各ページに応じて  $N_{PBF}$  の値を調整する。図 10 は、ターゲット時間が 7 日、書き換え回数が 100 回における各ページに注入すべきビットエラーの量を示している。図 10 のような各ページの  $N_{PBF}$  はターゲット時間と書き換え回数から選択されるように PBF テーブルへ格納される。各ページに対応した PBF テーブルを作成することで寿命のばらつきを削減できると考えられる。

$\boxtimes$  9  $N_{PBF}$  page-allocation scheme

図 10 PBF テーブルに格納される各ページの  $N_{PBE}$

図 11 に  $N_{PBF}$  page-allocation scheme を含めた際の PBF テーブルを示す。選択できるデータ寿命が 10 パターンとした場合、テーブルサイズは 128Gb チップ内の 0.01%にも満たない大きさである。

| Page<br>number            | Data<br>lifetime | Write/erase cycle | N <sub>PBF</sub> | (9 + 4 + 7 + 6)<br>×                                 |

|---------------------------|------------------|-------------------|------------------|------------------------------------------------------|

| 9 bit<br>:                | :<br>4 bit<br>:  | 7 bit<br>:        | 6 bit<br>:       | (258 ×10×100)<br>≒819KB (< 0.01%<br>of a 128Gb chip) |

| 258<br>pages<br>(1 Block) | 10<br>pattern    | 100<br>pattern    |                  | • • • • • • • • • • • • • • • • • • • •              |

図 11 PBF テーブル

#### 4. まとめと今後の課題

TLC NAND 型フラッシュメモリの寿命を制御するコントローラの構成に Partial bit-flip (PBF) と  $N_{PBF}$  page-allocation scheme を提案した。 PBF は、所定の寿命で誤り訂正限界に達するように書き込み前にビットを反転させる手法であり、 $N_{PBF}$  page-allocation scheme は、書き換え回数とターゲット寿命、ページ番号から反転させるビット数を決定する手法である。

今後の展望として、NAND型フラッシュメモリのサイズ、多値化の条件を変更し、データ寿命の制御をより正確に行える条件や、データ保持温度によるデータ寿命の制御への影響を調査する必要がある。

#### 参考文献

- [1] http://www.ftc.gov/system/files/documents/public\_statements/617191/150106cesspeech.pdf

- [2] http://ec.europa.eu/justice/data-protection/

- [3] http://aws.amazon.com/s3/details/

- [4] F. Masaoka et al. "New ultra high density EPROM

- and flash EEPROM with NAND structure cell," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, pp.552-555, Dec. 1987.

- [5] I. –J. Chang *et al.*, "Bit-error rate improvement of TLC NAND Flash using state re-ordering," *IEICE ELEX*, pp.1775-1779, 2012.

- [6] G. J. Hemink et al., "Trapped hole enhanced stress induced leakage currents in NAND EEPROM tunnel oxides," in: Proc. IEEE Int. Reliability Physics Symposium, Apr.,1996. pp. 117–21.

- [7] http://www.imation.co.jp/products/pdf/SSD\_WP 02.pdf, 2013

- [8] S. Yamazaki et al, ".Reliability Enhancement of 1Xnm TLC for Cold Flash and Milennium Memories," Symp. VLSI Circ., pp.T112-T113, 2015.

#### 関連する発表文献

#### 国際会議

- [1] Shuhei Tanakamaru, <u>Hiroki Yamazawa</u> and Ken Takeuchi, "Privacy-Protection Solid-State Storage (PP-SSS) System: Automatic Lifetime Management of Internet-Data's Right to be Forgotten," *IEEE Symposium on VLSI Circuit*, 2015

- [2] <u>Hiroki Yamazawa</u>, Kazuki Maeda, Tomoko Ogura Iwasaki and Ken Takeuchi, "Privacy-Protection SSD with Precision ECC and Crush Techniques for 15.5× Improved Data-Lifetime Control" *IEEE International Memory Workshop (IMW)*, 2016. (Submitted)

#### 国内会議

- [1] 前田一輝、<u>山沢裕紀</u>、竹内健 「プライバシー保護に向けた NAND 型フラッシュメモリの信頼性評価」、平成 27 年 12 月電子情報通信学会 ICD 研究会、ICD2015-74、pp47-47、2015 年 12 月

- [2] 前田一輝、田中丸周平、<u>山沢裕紀</u>、竹内健、「プライバシー保護に向けたソリッドステートシステム」、第63回応用物理学関係連合講演会、2016年3月(発表予定)