## マルチJTAGアダプタでCPUデバッグから FPGAコンフィグレーションまで自由自在

第6回[最終回]

FPGA/CPLDからのフラッシュ ROMの書き換え

細渕 憲行

連載第3回では、バウンダリ・スキャン機能を使ってCPUの外部バスに接続したフラッシュ ROMを JTAG 経由で書き換える方法について解説した。ここでは外部バスのピン配置が決まっていない、CPLDや FPGA に接続されたフラッシュ ROM を書き換える方法について解説する. (編集部)

## 1. UrJTAGの初期設定

今回は連載第3回(2010年11月号,pp.150-155)で紹介したJTAG操作ツール UrJTAGを使って、FPGAやCPLDに接続されたフラッシュ ROMを書き換えます。連載第3回で紹介したCPUに接続するフラッシュ ROMのときとは異なり、FPGAなどのプログラマブル・デバイスは、任意のピンにフラッシュ ROMの信号を自由に割り当てられます。UrJTAGはこの対応を定義することにより、簡易的な非同期バスを実現できます。今回はこの機能を使い、FPGA評価ボードに搭載されているフラッシュ ROMを書き換えてみます。

なお、UrJTAGのインストールとフラッシュ ROMの基本手順については、連載第3回の内容を参照してください。

## ● FPGA評価ボード

FPGA評価ボードとしては、本誌でおなじみの組み込みシステム開発評価キット(通称BLANCA)を取り上げる

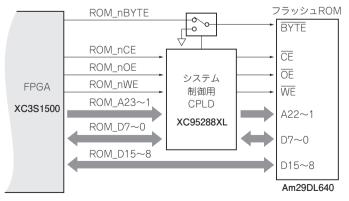

図1 システム開発評価キット (通称BLANCA) フラッシュ ROM 周辺の 構成

ことにします. このFPGA評価ボードには、一つのCPLD (XC95288XL) と二つのFPGA (XC3S1500とXC3S400) が搭載されており、フラッシュ ROM (Am29DL640G) は、CPLD からも FPGA (XC3S1500) からもアクセスが可能です.

BLANCAのフラッシュ ROM 周辺の構成を図1に示します。CPLDはシステム制御用で、標準状態ではXC3S 1500側からのフラッシュ ROMへのアクセスを仲介する動作となっています。よって、CPLDのバウンダリ・スキャンを操作すれば8ビット幅でフラッシュ ROMへ、CPLDを標準動作状態にさせてFPGAのバウンダリ・スキャンを操作すれば8ビットまたは16ビット幅でフラッシュ ROMへアクセス可能です。

以上のように、複数のデバイスから8ビット幅または16ビット幅でアクセスできるので、今回のテストにはうってつけのボードといえます.

## ● BSDLファイルの登録

まずBLANCAとマルチJTAGアダプタを接続し、UrJTAGからJTAGチェーンを見てみましょう。UrJTAGをインストールしただけの状態で、detectコマンドでデバイスを検出した結果を図2に示します。

JTAGチェーン上に三つのデバイスが存在します. そのうちの二つはXC3S400とXC3S1500として認識されていますが、残り一つの米国Xilinx社のデバイスXC95288XLが認識できていません. UrJTAGのデータ・ベースに存在していないためです. BSDL (Boundary Scan Description Language)ファイルを使ってこのデバイスを認識できるようにします.

UrJTAGにBSDLファイルを読ませるため、サーチ・パスを設定します。デフォルトではサーチ・パスが設定されてません。コマンドは次のようになります。