# cadence

## Virtuoso System Design Platform

Unified "system-aware" platform for IC and package design

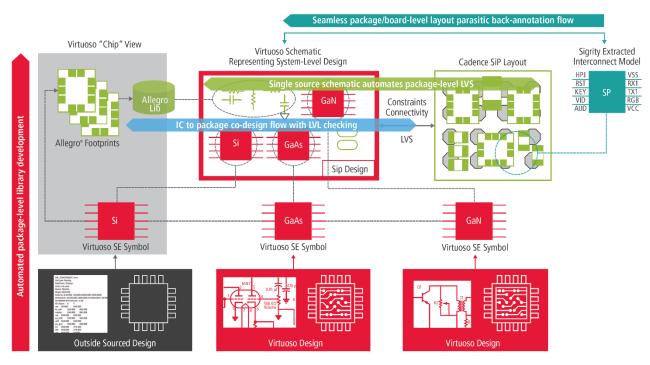

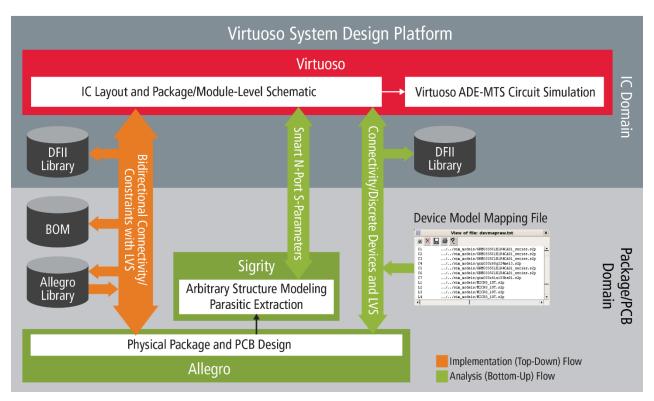

Cadence® Virtuoso® System Design Platform は、単一の回路図から IC およびパッケージのシミュレーションや LVS クリーンなレイアウトを促進する機能を提供するシステムベース・ソリューションです。このソリューションの中には、インプリメンテーションと解析の二つの主要なフローがあります。インプリメンテーション・フローでは、Virtuoso Schematic Editor 上で IC パッケージの回路図を作成した後、レイアウト・デザインを作成するためにこのデータを Cadence SiP Layout への変換が可能です。さらに、このフローの中では、ライブラリ部品の生成と検証、部品表(BOM)の出力、および、LVS チェックを実行することが可能です。解析フローでは、レイアウト・デザインの状況に関係なく、システム(IC-package-PCB)の任意の部分の抽出とシミュレーションが可能です。さらに、このフローは、PCB や IC パッケージの回路図を自動生成し、IC パッケージのインスタンスを IC の回路図やモデルにバインドし、Virtuoso ADE Product Suite と Spectre® Multi-Mode Simulation を使ってシステムをシミュレーションするためのテストベンチの構築を可能にします。PCB や IC パッケージのレイアウトから抽出された Cadence Sigrity でモデルは、生成された回路図に自動的にスティッチされます。

図 1. Virtuoso System Design Platform Flow

#### Introduction

既にパッケージに配置され PCB に置かれているチップが全ての製品仕様を満たすように設計することは、非常に困難が伴う作業です。近年のヘテロジニアスな統合の増加により、シングル・パッケージに統合してから PCB に統合する複数のテクノロジーにわたるマルチ・チップのデザインを考慮することが必要となります。十分な経験を持った設計者でも、これは大きな課題になる可能性があります。

今日、システム・レベル(IC-package-PCB)の設計では、チップのパフォーマンスや信頼性に関して、パッケージや PCB の工程での影響に関する多くの知識に基づく推測を必要とします。Virtuoso System Design Platform は、システム・レベルの影響を考慮したチップ設計から、この推測を排除します。

従来、アナログ/RF IC の設計者は、パッケージや PCB の影 響を考慮せずに IC 単体でシミュレーションしていました。 パッ ケージには、単一もしくは複数の IC とインターコネクトが含ま れています。また、IC が機能するために必要なディスクリート 部品が含まれていることも予想されます。同様に、PCBは、複 数のパッケージやインターコネクト、および、ディスクリート部 品を含みます。周波数が高くなると、性能を正確に把握する ためには、システム全体を一緒にシミュレーションすることが 重要です。IC 設計者とパッケージの設計者は、異なる回路図 エントリー・ツールを使用しています。そのため、IC 設計者は、 組み合わせたシステム・シミュレーションを実行するためには、 IC 回路図周辺のテストベンチとしてパッケージのシステム回 路図を再度作成する必要があります。以前は、その様なシス テム解析は、手作業によりパッケージ・モデルをシステム回路 図の部品に割り当てていました。この作業は、多くの間違い が生じやすいという課題があります。デザインの初期段階や テープアウトのかなり前に、この様なエラーを見つけ取り除く には、自動的に PCB やパッケージ全体とその寄生情報を含 み IC をシミュレーションすることを可能にする IC 設計者に使 い慣れた設計/シミュレーション環境が不可欠です。デジタ ル IC 向けの、その様な I/O や I/O インターコネクトをシミュ レーションする環境は存在します。一方、Virtuoso System Design Platform は、PCB/パッケージ、回路の寄生情報を含 みアナログ/RF IC のシミュレーションが可能なシームレスなフ ローを実現する、最初のソリューションです。このフローは、IC デザイナーを支援し、設計のイタレーションを最小化すること を可能にします。

Virtuoso System Design Platform は、トップ・ダウンのインプリメンテーション・フローとボトム・アップの解析フローの、両方を備えた IC を中心とした設計ソリューションを提供します。 Virtuoso System Design Platform の解析フローを使用することは、PCB やパッケージおよび電磁界シミュレーションについて最小限の知識しか必要としないで、完全なシミュレーション環境の実現に役立ちます。このような統合ソリューションにより、生産性の大幅な向上が予測されます。

Virtuoso System Design Platform のインプリメンテーション・フローは、単一の回路図エディタから IC レイアウトとパッケージ・レイアウトの設計につなげる機能を提供します。プリレイアウトのシステムシミュレーション (IC とパッケージを一緒に)の実行や、その後の各分野のレイアウトのインプリメンテーションにつなげる共通の環境によるシステムレベル・デザインを

#### Unification of the Virtuoso and Allegro/Sigrity Platforms

図 2. IC、パッケージ、PCB の関係

実行するために、同じ回路図エディタ(Virtuoso Schematic Editor)を使用することで、IC 設計者は、より優位なポジションにあると言えます。このフローは、SiP Layout で使用されるダイのフットプリントを生成することでパッケージ・レベルのライブラリ開発の多くの工程を自動化します。上級者は、ダイとパッケージを簡単に協調設計し、より良いパッケージ・レベルの配線やワイヤー・ボンディングの実現が可能です。

Virtuoso System Design Platform の解析フローは、S-パラメータや SPICE で与えられている寄生情報のモデルを持った PCB およびパッケージ・レイアウトを IC の設計環境に取り込むことを可能します。このフローでは、PCB やパッケージの接続情報を読み込み寄生情報モデルが与えらえている回路図を作成します。回路図は、PCB やパッケージ・システムの情報を含みシミュレーションすることが可能になります。

Virtuoso System Design Platform の設計環境は、パッケージや PCB のインターコネクトや外部部品の全てを IC にインテグレートしシミュレーションすることを実現します。これは、非常に重要なことです。なぜならば、通常、IC、パッケージ、PCBは地理的に異なる場所で、それぞれ独立に、デザイン・サイクルの異なるステージで、異なる設計ツールを使用して、異なるチームにより設計されます。Virtuoso System Design Platformは、パッケージ・レベルのレイアウトの寄生情報を共通の回路図にまとめ、システム全体のそれぞれの分野に共通のシミュレーションを可能にします。これにより、設計者は、テープアウト前に、性能に重大な違反があるかどうか特定することが可能です。必要な修正の情報は、パッケージ/PCB チームに直接伝達されます。

ここでの重要な機能は、シミュレーションの回路図に寄生情報 モデルを賢く取り込むことです。もしモデルにディスクリート・ デバイスが含まれている場合は、シミュレーション時に重複し て取り込まれない様にシミュレーション回路図の作成時に、そ れらを自動的にフィルタリングする必要があります。

### Virtuoso System Design Platform

Virtuoso System Design Platform フローは、IC、パッケージ、PCB および EM ソルバーの分野について、以下のプロダクトの機能を通して実現します。

- Virtuoso Schematic Editor: パッケージ回路図の作成

- Virtuoso Layout Suite: ダイのエクスポート

- Cadence SiP Layout XL: マルチ・ダイ・パッケージの設計 とレイアウト作成

- Sigrity EM solvers : PCB とパッケージのモデル抽出

- Spectre Multi-Mode Simulation: システム・シミュレーション

Virtuoso System Design Platform にはインプリメンテーション・フローと解析フローの、二つの主要なフローが存在します。インプリメンテーション・フローでは、パッケージ・レイアウト・エディタでの設計をする前に、Virtuoso Schematic Editor でパッケージの回路図を設計することを可能にします。さらに、Virtuoso Layout Suite からのダイ・フットプリントとシンボルの作成およびパッケージ回路図の構築にそれらを使用することが可能です。双方向なデータのやり取りは、SiP Layout に回路図の編集を動的に伝搬し、また、その逆も可能です。

BOM の生成、直感的な方法でのデザインの違いの可視化、 レイアウト・レポートの参照は、このフローのその他の重要な 機能の一部です。

上記のインプリメンテーション・フローを用いて、パッケージやPCBが設計されれば、解析フローにより、寄生モデルが自動的にスティッチされた部品と共にPCBやパッケージ・レイアウトを回路図としてVirtuoso環境に取り込み、設計サイクルの早い段階から明らかにすることで、寄生を考慮したシステムレベルのシミュレーションの実現を可能にします。その様なシステムをシミュレーションし、早期に性能の結果の重要な偏差を特定し、必要な修正をパッケージ・チームやPCBチームとやり取りすることを可能にします。

#### **Benefits**

Virtuoso、Allegro、Sigrity、Spectre のプラットフォームを統合することで、Virtuoso System Design Platform には、次の三つの主な利点を持っています。

● Virtuoso Schematic Editor を使用して、IC レイアウト・デザインやパッケージ・レイアウト・デザインを更新します。言い換えると、IC レイアウトに加えて、パッケージ・レイアウト

用の回路図を作成することが可能です。Virtuoso System Design Platform では、Virtuoso Schematic Editor は、単一の回路図エディタ・ドリブンの IC およびパッケージ設計 (a single schematic editor-driven IC and package design) 機能を提供します。

- マルチ・テクノロジー・シミュレーション機能と併せて、 Virtuoso Analog Design Environment でシミュレーションが 可能なパッケージや PCB の寄生情報が考慮された回路 図を作成することが可能です。これは、完全なシステムを 考慮したシミュレーションの実現に不可欠な機能です。

- 協調設計用ダイ・アブストラクト・フローにより、IC とパッケージを同時に設計することが可能です。この機能は、デザインのイタレーションを最小限に抑え、最新のフロアプランニングやデザインの実現可能性の問題を削減します。

#### **Features**

#### ダイ・アブストラクト機能

Virtuoso System Design Platform は、パッケージ回路図やパッケージ・レイアウトの構築に使用するフットプリントやシンボルの情報を Virtuoso レイアウトから生成するための重要な

図 3. Virtuoso System Design Platform フロー

図 4. ダイ・アブストラクト

機能が備わっています。この機能により、IC とパッケージ・レイアウトの同時協調設計が可能となり、設計のイタレーションを最小限に抑えます。

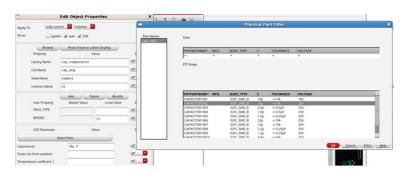

#### プロジェクト作成と部品テーブルファイルのアサイン機能

パッケージ回路図を作成する際に、ベンダーが供給する部品を効率的に選択することが不可欠です。部品テーブル・ファイルのオプションは、さまざまなベンダーからの百万もの部品からシームレスな選択を可能にし、それらを回路図のインスタンスに効率的に割り当てることが可能です。

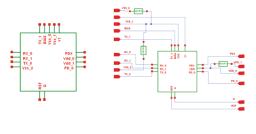

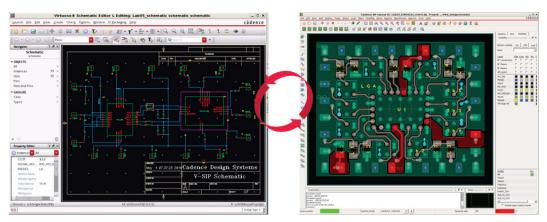

## 回路図情報の SiP Layout への受け渡し機能

全ての部品を含む回路図が作成されれば、回路図情報をSiP Layout エディタにシームレスに転送することができます。その後、SiP Layout エディタ上で全ての部品を配置し、配線を作成し、最終的なパッケージを完成させることができます。

# SiP Layout の編集と Virtuoso Schematic Editor へのパック・アノテート機能

設計サイクルの中で、レイアウト設計者が Virtuoso Schematic Editorでマッチさせることが必要な変更について提案する可能性が十分にあります。この機能は、Virtuoso Schematic Editor にシームレスに情報の受け渡し回路図とレイアウトが常に同期することを可能にします。

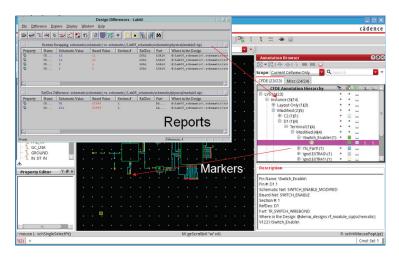

## 異なるレイアウトと回路図のデザイン・チェック機能

ネットやコンポーネント、レイアウトと回路図の違いをハイライトするサインオフ品質の LVS チェック機能を備えています。さらに、デザインのショート、レイアウト上に配置されていない部品のチェック、DRC チェックにも対応しています。Virtuoso Schematic Editor の Annotation Browser アシスタントを使用すれば、直感的にグラフィカルな方法により全ての差分がレポートされます。

#### BOM レポート生成機能

BOM レポートは、デザインで使用されている全ての部品と、各部品の異なるプロパティの部品番号および値をリストします。これは、OEM(相手先商標製品)にとって、極めて重要な入力です。Virtuoso System Design Platform は、この様な全てのレポートを生成するためのユーザー・フレンドリーな高度にカスタマイズ可能な環境を備えています。

図 5. 実装回路図の部品ファイルからのパッケージ・レベルの部品の選択

図 6.スケマティック・ドリブン・パッケージ・レイアウト

### **Analysis Flow Features**

## サード・パーティ・サポート

寄生を考慮した PCB/パッケージの回路図デザインに、サード・パーティ・ベンダーが供給する SMD のモデルのシームレスなインポートに対応しています。

- 寄生情報モデルを含むデザインライブラリ(SPICE および S-パラメータ)

- Virtuoso Layout Suite ダイ

- Allegro PCB/パッケージ・レイアウト

- PCB/パッケージのトレースおよびコンポーネントの寄生 情報モデルを表す Sigrity モデル

- SMD SiP レイアウトのデバイス・モデル

- Virtuoso Schematic Editor 回路図

- Parasitic-aware simulation 回路図

- Virtuoso Layout Suite で設計されたダイのフットプリント

### プラットフォーム/OS

- Virtuoso プラットフォームのツールは Linux 上で動作します。

- Allegro と Sigrity のツールは、Linux および Microsoft Windows 上で動作します。

## Virtuoso System Design Platform フローの実行に必要なツール

- Virtuoso Schematic Editor XL

- Virtuoso Layout Editor

- Virtuoso Analog Design Environment

- Spectre Multi-Mode Simulation, Spectre RF Option

- Allegro SiP および PCB レイアウト・エディタ

- Sigrity PowerSI®、Sigrity PowerSI 3D EM Extraction Option および Sigrity XtractIM™

#### Cadence Services and Support

● Cadence のアプリケーションエンジニアは、技術問い合わ

図 7. Viewing LVS differences highlighted in the Annotation Browser

せに回答いたします。Cadence では、テクニカルな支援や個別のトレーニングコースも用意しています。

- Internet Learning Series (iLS) のオンラインコースでは、インターネット経由で、自身のコンピュータ環境でトレーニングを自由に受講することができます。

- Cadence Online Support では、沢山の最新のソリューションや技術資料の参照や、ソフトウェアのダウンローが可能です。

- サポートについての詳細は、以下をご覧ください: https://www.cadence.com/support

- トレーニングについての詳細は、以下をご覧ください: <a href="https://www.cadence.com/training">https://www.cadence.com/training</a>

## cādence°

### 日本ケイデンス・デザイン・システムズ社

本社/〒222-0033 神奈川県横浜市港北区新横浜 2-100-45 営業本部

TEL.(045)475-8410 FAX.(045)475-8415

〒541-0054 大阪府大阪市中央区南本町 2-6-12 サンマリオン NBF タワー16F TEL.(06)6121-8095 FAX.(06)6121-7510

URL https://www.cadence.com/jp

© 2019 Cadence Design Systems, Inc. All rights reserved worldwide.

CadenceおよびCadenceロゴ は、Cadence Design Systems, Inc.の登録商標です。その他記載されている製品名および会社名は、各社の商標または登録商標です。

\* 掲載の内容は、2019 年 05 月現在のものです。

#### 販売代理店 イノテック株式会社 IC ソリューション本部

〒222-8580 神奈川県横浜市港北区新横浜 3-17-6 TEL\_(045)474-2290,2291,2293(営) FAX.(045)474-2395 〒541-0054 大阪府大阪市中央区南本町 2-6-12 サンマリオン NBF タワー16F TEL. (06)6121-7703(営) FAX. (06)6121-7720

TEL. (06)6121-//03(宮) FAX. (06)6121-/ URL <u>http://www.innotech.co.jp/</u>