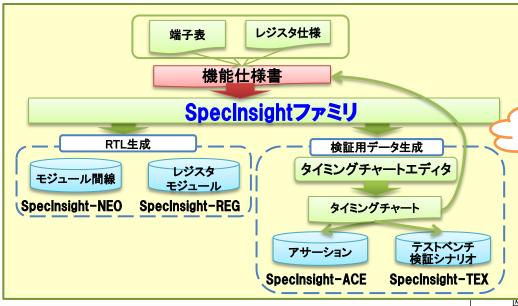

# 仕様書情報から設計検証データを自動生成!

## SpecInsight-NEO(モジュール間結線生成ツール)

### 【機能】

- ・入出力端子表(図1)と接続情報からモジュール間接続RTL(図2)を 自動生成します

- •RTL記述言語は、Verilog または VHDL から選択可能です

### 【特徴】

- ・入出力端子表、接続情報はExcelファイルで作成可能です お客様のフォーマットをそのまま使用することもできます

- ビット幅の不一致や入出力定義の不整合をチェックできます。

## 【効果】

・面倒で単純ミスが発生しやすいモジュール間接続作成から解放されます

【ムービーで見る】https://www.youtube.com/watch?feature=player\_embedded&v=XtLNzBQfKCA

### AO\_MSTRB 1'60 AO\_MREADY AXI7570 AO BVALID AO\_BREADY 0 AO\_ARADDR AO\_ARLEN

7.出力端子裏の例

|                                                                                                                                                         |                                                                                               | 八山川畑丁衣の例 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------|

| library IEEE use IEEE std use IEEE std use IEEE std entity al is port ( olk rst_x Al_AWID Al_AWID Al_AWIST Al_AWIST Al_AWIST Al_AWIST Al_AWIST Al_AWIST | _logio_116<br>_logic_ari<br>_logio_uns<br>: in<br>: in<br>: in<br>R : in<br>E : in<br>ST : in | th.all;  |

|                                                                                                                                                         |                                                                                               |          |

図2 RTL出力例

## SpecInsight-REG(レジスタモジュール生成ツール)

#### 【機能】

- ・レジスタ仕様(図3)からレジスタモジュールRTL(図4)を 自動生成します

- •RTL記述言語は、Verilog または VHDL から選択可能です

- ・バスインタフェースは標準バスをサポートします

#### 【特徴】

レジスタ名の重複やアドレスマップのミスをチェックできます -AXI、AHB、APBバスに対応します

### 【効果】

- レジスタ数が多くても、レジスタ仕様を定義すれば 簡単にRTLを生成できます

- 仕様書やRTLの形式を統一することができます

| ベースアド        |        | グ <u>ループ名</u> | ビット   | バス   | Reset | 接続      |                         |

|--------------|--------|---------------|-------|------|-------|---------|-------------------------|

| グ <u>ループ</u> | サイズ    | ブ <u>ロック名</u> | A.    | アクセス | 初期値   | 出力      |                         |

| ブロック         | (Byte) | フィールド名        | 7942  | 属性   | 非同期   | 内部F     |                         |

| 0×000        | 0400   | UART          |       |      |       |         | UARTコアのレジスタ・マップを示します。   |

|              | uxiuu  | OART          |       |      |       |         | を介してコアの制御と通信を行います。      |

| 0×00         |        | Data          |       |      |       |         | エンベデッボ・ソフトウェアは、Dataレジス  |

|              |        |               | [7:0] | EW   | _     | FWife   | す。                      |

|              |        |               | [7.0] | 1007 |       | TOTALIO | ライトすることで送信FIFOに書き込みが    |

|              |        |               |       |      |       |         | ₫.                      |

| 0x04         |        | Status        |       |      |       |         | エンベデッド・ソフトウェアは、Statusレジ |

|              |        |               |       |      |       |         | 送信FIFOがフルの場合TXFULL=1を返  |

|              |        | TXFULL        | [0]   | RO   |       | 1       | 込みは可能ですが、フル状態の間はDa      |

|              |        |               |       |      |       |         | L給けますので注意が必要です。         |

|              |        | RXVALIO       | [1]   | RO   |       | l .     | 受信FIFOに有効なデータがあるかどうた    |

|              | 1      | 1 1 2 2 2     | 111   |      |       |         | 受信FIFOIコラ以上の有効なデータがあ    |

図3 レジスタ仕様の例

レジスタモジュールTOP レジスタ バスIF レジスタ モジュール モジュール モジュール 構成概要

図4

## SpecInsight-ACE(アサーション自動生成ツール)

### 【機能】

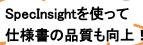

- ・専用エディタで仕様書(タイミングチャート)を作成できます(図5)

- ・タイミングチャート上にアサーション仕様を図で定義できます(図6)

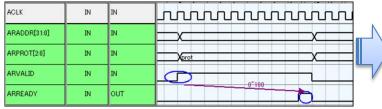

- ・アサーション仕様からSystemVerilog Assertion コード(図7)を生成します

### 【特徴】

- ・タイミングチャートを簡単に作成することができます

- •アサーション言語を知らなくてもアサーションを定義できます

- ・図で定義したアサーションを日本語の説明文として出力します

## 【効果】

- ・アサーション・ベース検証を簡単に導入することができます ※アサーションに関する詳しい知識は必要ありません

- 検証内容を図で表示できるので、レビューがしやすくなります

- タイミングチャートもアサーションも簡単に再利用できます。

図6 アサーション定義例

IN IN mmmmmm RESETr リセット ARADDR[31:0 IN リードアドレス RPROT[2:0] IN プロテクション RVALID IN ARREADY OUT レディ RDATA[31:0] RRESP[1:0] OUT 応答 OUT READY IN レディ 補足説明 ①ARVALIDアサート後、ARREADYは一定期間内に応答しなければならない(100サイクル以内)②RVALDIアサート後、RREAYは一定期間内に応答しなければならない(100サイクル以内)

図5 タイミングチャート例(仕様書用)

アサーショングループ名

READ\_ADR

アサーション表

AXIL\_LiteS\_ARREADY\_MAX\_WAIT

アサーション内容

ARVALIDがのから1(こ変化した時、のから100サイクル後、(ARREADY=1)とならなければならない

property p\_axi4\_lites\_arready\_max\_wait,

@(posedge\_ACLK)

((\$past(ARVALID)= 0)&&((\$stable(ARVALID)) && (ARVALID==1)) | >

##[0:100] (ARREADY == 1));

endproperty

AXI4\_LiteS\_ARREADY\_MAX\_WAIT: assert property(p\_axi4\_lites\_arready\_max\_wait)

else begin \_\_\_\_display("##### [ ERROR ] AXI4\_LiteS\_ARREADY\_MAX\_WAIT");

図7 アサーション・コードの出力例

【ムーピーで見る】タイミングチャート作成 https://www.youtube.com/watch?feature=player\_embedded&v=GnHS8gSLe6k アサーション作成 https://www.youtube.com/watch?feature=player\_embedded&v=Coe5i=84u\_s

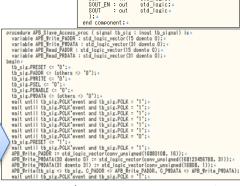

# SpecInsight-TEX(テストベンチ生成ツール)

#### 【機能】

- 仕様書用に作成したタイミングチャートから、テストベンチの入力情報を生成します

- 複数のタイミングチャートを組み合わせて検証シナリオを作成でき、テストベンチと 一緒に出力できます(図8)

- ・テストベンチ記述言語は、Verilog または VHDL から選択可能です

### 【特徴】

- タイミングチャートがあれば、簡単な操作でテストベンチを作成できます

- •RTLとテストベンチは入出力端子表から自動で接続します

- ■SpecInsight-ACEで生成したアサーションも簡単に取り込めます

### 【効果】

- テストベンチに不慣れな人でも簡単にシミュレーションを実行できます。

- 設計の初期段階で簡単にシミュレーションによる動作確認ができます

【ムービーで見る】https://www.youtube.com/watch?v=5GlsIE56SF0&feature=player\_embedded

| 機能          | 製品名                   | 備考                          |  |

|-------------|-----------------------|-----------------------------|--|

| ᇚᇿᄽᆄ        | SpecInsight-NEO       |                             |  |

| RTL生成       | SpecInsight-REG       |                             |  |

| アサーション生成    | SpecInsight-ACE       | _(*)タイミングチャート<br>エディタ単体もご購入 |  |

| テストベンチ生成    | SpecInsight-TEX       |                             |  |

| タイミングチャート作成 | SpecInsight-タイミングチャート | いただけます                      |  |

### TIBLOP is and entity:

architecture RIL of TB\_TOP is a component apb a port (...)

PCLK in std\_logic; \*

PRESET in std\_logic; \*

PENABLE in std\_logic; \*

PENABLE in std\_logic; \*

PENABLE in std\_logic; \*

PODATA in std\_logic; \*

PENABLE in std\_logic; \*

PODATA in std\_logic; \*

PENABLE in std\_logic; \*

PODATA in std\_logic; \*

PENABLE in std\_logic; \*

PENABLE in std\_logic; \*

PODATA in std\_logic; \*

PENABLE in std\_logic; \*

PENABLE in std\_logic; \*

PENABLE in std\_logic; \*

PENABLE in std\_logic; \*

STM\_ENABLE in std\_

図8 タイミングチャートとテストベンチ出力例

製品紹介の 動画が見れます!

各製品は、予告なく変更する場合があります 2015年5月 Rev1.4

### ■新横浜本社

E-mail

住所 横浜市港北区新横浜2-3-12 TEL 045-477-2005

info\_pal@paltek.co.jp